手机时钟信号是什么意思

手机的时钟信号是时序逻辑的基础,一般的数字电路都工作在一定的时序下,时序由时钟信号决定,且时钟信号一般有其自身固有的频率

同时时钟信号由特定的电路产生,只由自身的晶体震荡器决定。如果手机没有时钟信号,手机就会停止工作。

(四)脉冲信号和时钟信号

波形是脉冲的电压或电流,通常就把一切既非直流又非正弦交流的电压或电流统称为脉冲电

电脉冲

脉冲电流其中的一个周期过程就可以看成一个电脉冲,可以当成信号的一次发出

相对于连续信号在整个信号周期内短时间发生的信号,大部分信号周期内没有信号。就象人的脉搏一样。现在一般指数字信号,它已经是一个周期内有一半时间(甚至更长时间)有信号。计算机内的信号就是脉冲信号,又叫数字信号

脉冲电路是专门用来产生电脉冲和对电脉冲进行放大、变换和整形的电路

利用脉冲整形的程序可以产生不同的脉冲形状,根据应用的不同,最佳的脉冲形状也随之不同。

在数字电路(计算机)中分别以高电平和低电平表示1状态和0状态。此时电信号的波形是非正弦波,为 脉冲信号,又叫数字信号

说法1:在时序逻辑电路中,为了控制各触发器同步协调一致的工作,通常需要一个稳定精确的时钟脉冲信号

说法2:在同步时序电路中, 作为时钟信号的矩形脉冲 控制和协调着整个系统的工作

在内部循环周期小于最坏情况下的内部传播延迟时,大多数足够复杂集成电路使用时钟信号同步电路的不同部分

引用知乎上的一个解释:

CPU里可以粗略的认为是很多很多很多小电容(充满电了算1,没充电算0),每次计算就是这些小电容翻来覆去的充电放电。

很多小电容组成一个个基本的模块,比如输入到输出。输入到输出是有延迟的,因为前面说了,电容要充电放电,这个需要时间。

基本小模块各种连接,组成复杂的功能,也就是前面小模块的输出会被后面模块当成输入。

模块连接行成功能,那么后面的模块要如何知道前面的模块到底是已经完成充电/放电了呢,还是正在充电放电呢?另一方面,路径越长从最开始输入到最终的输出的时间就越长,也就是路径长度不同延迟就不同,所以你很难保证每个针脚上的数据严格的同时到达。

所以就引入了时钟机制:用一个统一的时钟脉冲来同步各个小模块。脉冲没来,小模块抓紧时间充电放电,脉冲来了,模块一起动。可以简单的认为时钟脉冲来一下,CPU就动一下。下个时钟脉冲一直不来,CPU就一直不动

(保证运算时,数据的读-写-计算必须要严格的按照顺序依次进行)

时钟边沿触发信号意味着所有的状态变化都发生在时钟边沿到来时刻。只有当同步信号到达时,相关的触发器才会按输入信号改变输出状态,使得相关的电子组件得以同步运作。控制逻辑单元状态量变化的是时钟信号的上升沿还是下降沿,取决于具体的逻辑设计

时钟不是作用在ALU(逻辑控制单元)上而是寄存器上 ,这种特殊的寄存器叫:时钟寄存器。只有在时钟信号的上升沿(比如说5V高位)才能往里写入。其他时候,输入只能在外面等着

时钟频率(又译: 时脉速度 ,英语: clock rate ),是指同步电路中时钟的基础频率,它以“若干次周期每秒”来度量,量度单位采用SI单位-赫兹(Hz)。它是评定CPU性能的重要指标。

例如,来自晶振的基准频率通常等于一个固定的正弦波形,则时钟频率就是这个基准频率,电子电路会为数字电子设备将它转化成对应的脉冲方波。

时钟信号是矩形脉冲,获取矩形脉冲的途径不外乎两种:

当然,在采用整形的方法获取矩形脉冲时,是以能够找到频率和幅度都符合要求的一种已有电压信号为前提的。

时钟信号定义?

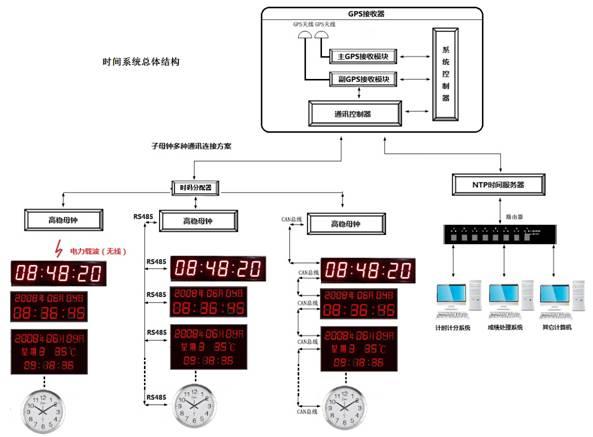

时钟信号是时序逻辑的基础,它用于决定逻辑单元中的状态何时更新。时钟信号是指有固定周期并与运行无关的信号量,时钟频率(clock frequency,CF)是时钟周期的倒数。

什么是时钟信号?时钟信号的作用,和工作原理?

时钟信号是时序逻辑的基础,用于决定逻辑单元中的状态何时更新,是有固定周期并与运行无关的信号量。时钟信号有固定的时钟频率,时钟频率是时钟周期的倒数。

作用:时钟信号通常被用于同步电路当中,扮演计时器的角色,保证相关的电子组件得以同步运作;可以使用时钟来同步 CPU 的不同进程,通过上升沿或下降沿来改变周期输出。

工作原理:定时信号是从传输的数字信号中提取出来的。对于某些接收信号,经频谱分析没有离散定时频率谱线,非线性处理电路是使处理后的信号具有离散定时频率谱线。预滤波器在某些系统中用来减小定时信号相位抖动。窄带滤波器的提纯作用可用锁相环路实现,也可得到定时信号。

扩展资料:

时钟信号的高电平和低电平状态

时钟信号能表示一种特殊信号振荡之间的高和低的状态,信号的利用像一个节拍器协调行动的数字电路,数字时钟信号基本上是方波电压。时钟信号是由时钟发生器产生的。它有只有两个电平,一是低电平,另一个是高电平。高电平可以根据电路的要求而不同,例如 TTL 标准的高电平是 5V。

最常见的时钟信号是在与 50%的占空比,高电平和低电平的持续时间是一样的,通常是一个固定的常数频率方波的形式。电路使用时钟信号的同步可能会变得活跃在任一上升沿,下降沿,或在双数据速率,在上升和下降边缘的时钟周期,可以根据数字电路使用需要提供出任何时钟频率。

参考资料来源:百度百科-时钟信号